## Advanced Packaging: Integration in die SMT-Produktion

# SMDs und Dies auf einer Fertigungslinie

**Im Zeitalter von Advanced Packaging und hochintegrierten SiP-Modulen lösen sich die traditionellen Trennlinien zwischen Halbleiter-Backend-Fertigung und SMT-Prozessen zunehmend auf. ASMPT hat Plattformen im Portfolio, die das Produktionsspektrum auf dieses neue Niveau heben: Neben dem Lotpastendrucker DEK Galaxy sind es die hochinnovative Bestückplattform SIPLACE TX micron und allen voran die wegweisende hybride Bestückplattform SIPLACE CA2, die in der Branche völlig neue Maßstäbe setzt.**

Bevor Advanced Packaging Einzug hielt, war die Rollenverteilung in der Elektronikproduktion eindeutig: Die SMT-Fertigung war auf hohe Taktzahlen und maximale Geschwindigkeit ausgelegt, während in der Halbleiterproduktion Präzision oberste Priorität hatte. Kein Wunder – die Kontaktstellen auf einem Die sind um ein Vielfaches kleiner als klassische SMD-Lötstellen, und die Abstände zwischen den Komponenten fielen großzügiger aus. Erst durch die Backend-Prozesse konnte eine zuverlässige Verbindung zwischen den feinen Strukturen des Dies und den auf SMD-Größen skalierten Kontaktflächen hergestellt werden – eine essenzielle Voraussetzung für die Integration in die Hochgeschwindigkeits-SMT-Fertigung.

In der traditionell getrennten Elektronikwelt bedeutete neue Funktion oft: neuer Chip – ein extrem teurer und langwieriger Entwicklungsprozess. Heute geht es effizienter: Statt alles neu zu entwickeln, werden bewährte Chips zu einem leistungsfähigen Modul kombiniert. Ergänzt um Standardkomponenten in SMD-Bauform, entstehen so System-in-Package-Module (SiP), in denen Dies und SMDs gemeinsam in einem Gehäuse arbeiten. Ein anschauliches Beispiel dafür, wie die Grenzen zwischen Halbleiter- und SMT-Fertigung zunehmend verschwinden.

SiP-Module müssen aber nicht nur funktionieren, sondern auch wirtschaftlich in großer Stückzahl gefertigt werden können. Was liegt also näher, als die Die-Verarbeitung direkt in die SMT-Linie zu integrieren? Doch das scheiterte lange an der technischen Realität: Konventionelle Bestückautomaten und Lotpastendrucker waren schlicht zu unpräzise – und klassische Die-Bonder zu langsam für die Taktzahlen moderner SMT-Linien.

ASMPT erkannte früh, dass es neue Lösungen braucht. Als Technologiepionier und Marktführer mit starker Präsenz in beiden Welten – Halbleiter wie SMT – gelang

es dem Unternehmen, die Prozessgrenzen zu überwinden. Das Ergebnis: Plattformen, die beide Technologien erstmals nahtlos vereinen.

### DEK Galaxy: Advanced Packaging trifft hochpräzisen Lotpastendruck

Ein Beispiel für die gelungene Integration von Advanced Packaging in bestehende SMT-Prozesse ist der Lotpastendrucker DEK Galaxy. Die Plattform kombiniert hohe Leistung mit bemerkenswerter Flexibilität und erlaubt schnelle Produktwechsel bei gleichzeitig stabilen Prozessen. Mit einer Nassdruckgenauigkeit von >2,0 cpk bei  $\pm 17,5 \mu\text{m}$  ( $\pm 6 \sigma$ ) ist der DEK Galaxy sowohl für Wafer Bumping per Lotpastendruck als auch für die SMT-Vorbestückung hochkomplexer Baugruppen geeignet. Auch DirEkt Ball Attach auf Wafern und Substraten mit Kugeldurchmessern bis hinunter auf 0,2 mm beherrscht das System zuverlässig – und empfiehlt sich damit als zentrale Komponente für durchgängig hybride Fertigungslinien.

Der DEK Galaxy bietet eine Vielzahl an Optionen, die ihn besonders für Advanced Packaging prädestinieren. Durch den Einsatz von Singulated Tooling Systems wie DEK Virtual Panel Tooling oder MASS können mehrere individuelle Substrate in einem einzigen Druckzyklus verarbeitet werden. Für die Substrat- und Waferverarbeitung unterstützt die Plattform JEDEC-konforme Wafer-Chucks und Carrier-Standards. Eine optimale Leiterplattenunterstützung – selbst bei hoher Bauelementdichte – ermöglichen Grid-Lok® sowie individuell anpassbare Tools. Auch für spezielle Anwendungen wie den 3D-Schablonendruck mit AgS-Paste im Power Electronics Packaging ist die Maschine bestens geeignet.

Trotz seiner hohen Präzision und Flexibilität bleibt der DEK Galaxy schnell: Linearmotoren und das neu entwickelte Hochgeschwindigkeits-Schablonenreinigungssystem DEK Typhoon sorgen für eine Kernzykluszeit von nur sieben Sekunden – und damit für uneingeschränkte Taktzeitfähigkeit auch in modernen Highspeed-Linien.

### SIPLACE TX micron: Höchste Präzision für SiP- und High-Density-Anwendungen

Mit der SIPLACE TX micron präsentiert ASMPT eine Bestückplattform, die speziell für anspruchsvolle

Advanced-Packaging- und High-Density-Anwendungen entwickelt wurde. Die Maschine überwindet bisherige Grenzen bei Bestückgenauigkeit und -geschwindigkeit – dank dem Zusammenspiel aus temperaturstabilen Glaskeramik-Skalen, präziser Passmarkenerkennung, hochauflösenden Bildverarbeitungssystemen und Vakuum-Toolings. Das Ergebnis: eine Platziergenauigkeit von bis zu  $\pm 10 \mu\text{m}$  – kombiniert mit einer maximalen Leistung von bis zu 93.000 Bauteilen pro Stunde.

Die SIPLACE TX micron ist für die Verarbeitung empfindlichster Komponenten optimiert. Der vollständig programmierbare Bestückprozess umfasst Features wie Touchless Pick-up, Zero Force Placement sowie eine lückenlose Rückverfolgbarkeit – vom Tape bis zum Endprodukt. Ein hochauflösendes Vision-System erkennt kleinste Risse oder Schäden bei voller Geschwindigkeit und sortiert fehlerhafte Bauelemente frühzeitig aus. Für den Einsatz unter kontrollierten Bedingungen ist die Plattform nach Reinraumklasse 7 (DIN EN ISO 14644-1) sowie SEMI S2/S8 zertifiziert.

Auch im Produktionsalltag zeigt die SIPLACE TX micron ihre Stärken: Eine hochauflösende Leiterplattenkamera, der Multi Purpose Dual Conveyor mit flexiblen Transportoptionen sowie die Nonstop-Zuführung von Bauelementen in JEDEC-Trays über die SIPLACE Tray Unit gewährleisten einen maximalen Ertrag. Ergänzt wird die Plattform durch eine leistungsstarke Steuerungssoftware, die eine präzise Prozessführung und eine konstant hohe Bestückqualität sicherstellt – auch bei hohen Durchsätzen und variierenden Produktanforderungen.

#### **SIPLACE CA2: Hybride Highspeed-Plattform für Dies und SMDs**

Einen echten Quantensprung im Bereich Advanced Packaging markiert die SIPLACE CA2. Mit dieser revolutionären Hybrid-Plattform beweist ASMPT einmal mehr seine Markt- und Technologieführerschaft. Die SIPLACE CA2 ergänzt die SIPLACE TX micron optimal und bringt als Kombination aus SMT-Bestückautomat und Die-Bonder maximale Flexibilität in die Linie. In einem einzigen Arbeitsgang verarbeitet sie sowohl SMDs, die über Wechseltische oder Förderer zugeführt werden, als auch Dies direkt vom gesägten Wafer. Damit lässt sich der komplette Die-Bonding-Prozess direkt in die SMT-Linie integrieren. Aufwendige externe Prozessschritte wie Die Taping entfallen ebenso wie der Einsatz spezialisierter Einzelmaschinen. Das spart nicht nur Platz und Kosten, sondern reduziert auch Rüstaufwand, Nachfüllzeiten und Gurtabfall erheblich. Darüber hinaus ist die direkte Verarbeitung vom Wafer für empfindliche Dies deutlich schonender und minimiert das Risiko von Bauelementenschäden – ein klarer Vorteil gegenüber der klassischen Gurtzuführung.

Ein Wechselsystem erlaubt die Handhabung von bis zu 50 verschiedenen Wafern für Flip-Chip- und Die-Attach-Montage, mit einem Wafer-Swap in nur 13 Sekunden. Gleichzeitig können ein Wafer-Chuck, eine Flux-Dipping-Unit (LDU) und zehn 8-mm-Tape-and-Reel-Feeder-Tracks parallel betrieben werden – für maximale Flexibilität bei hoher Taktleistung. Ein Novum in der Halbleiterverarbeitung: Tracedaten jedes einzelnen Dies ermöglichen eine lückenlose Rückverfolgbarkeit vom Wafer bis zur Bestückposition auf der Leiterplatte – ein wesentlicher Beitrag zur Qualitätssicherung und Prozesskontrolle.

Die Integration der Die-Verarbeitung in die SIPLACE CA2 erforderte eine vollständige Neuentwicklung – denn konventionelle Verfahren aus der Halbleiterfertigung hätten den Durchsatz einer SMD-Linie deutlich ausgebremst. Der Hintergrund: Dies werden bereits gesägt auf Trägerfolien (Wafer Film Frame) angeliefert und müssen noch vereinzelt werden. Dabei wird das Die mithilfe einer Ausstechnadel, die von unten durch die Trägerfolie stößt, leicht angehoben, während die Folie gleichzeitig mittels Unterdruck entgegengesetzt bewegt wird. Aufgrund der hohen Bruchempfindlichkeit der Dies, in Abhängigkeit von deren Geometrie und Materialeigenschaften, ist dieser Ablösevorgang technisch nur begrenzt beschleunigbar und somit bei serieller Abarbeitung der zeitbestimmende Prozess. Die Lösung: Ein intelligentes Puffersystem, das nach dem Prinzip eines Collect-and-Place-Bestückkopfs arbeitet. Während die Dies schonend vereinzelt und zwischengespeichert werden, läuft die Bestückung ohne Unterbrechung weiter. Durch die Parallelisierung von Ablösung und Platzierung erreicht die SIPLACE CA2 eine Leistung von bis zu 54.000 Dies und 76.000 SMDs pro Stunde – bei einer Platziergenauigkeit von bis zu  $\pm 10 \mu\text{m}$  @  $3\sigma$ . Damit ist die Hybrid-Plattform auch für moderne Highspeed-Linien bestens geeignet.

#### **System-in-Package: Schlüsseltechnologie für neue Märkte**

Ob smarte Devices, 5G-Kommunikation, autonomes Fahren oder Künstliche Intelligenz – all diese Technologien erfordern hochintegrierte, leistungsfähige und zugleich kompakte elektronische Systeme. Möglich wird das nur durch eine konsequente Miniaturisierung, bei gleichzeitig wachsender funktionaler Dichte auf Bauelementebene.

Eine Schlüsselrolle übernimmt dabei die System-in-Package-Technologie (SiP). Sie erlaubt es, unterschiedliche Chips – etwa Logik, Speicher, RF, Sensorik oder Leistungselektronik – gemeinsam mit passiven SMD-Komponenten in einem einzigen Bauelementgehäuse zu integrieren. So entstehen hochfunktionale Module mit kurzer Signalführung, reduziertem Platzbedarf und verbesserter elektrischer Performance.

Für die Fertigung bedeutet das einen Paradigmenwechsel: SiP-Module verlangen eine nahtlose Verbindung von Halbleiterprozessen wie Die-Bonding und Wafer-Verarbeitung mit SMT-typischen Abläufen wie Lotpastendruck und SMD-Bestückung. Die Folge: Das Auftragsspektrum der SMD-Fertigung wird deutlich ausgeweitet – hinein in Bereiche, die bisher reinen Halbleiterlinien vorbehalten waren.

Damit SiP wirtschaftlich produziert werden kann, müssen diese hochpräzisen Prozesse nicht nur exakt aufeinander abgestimmt, sondern auch mit hoher Taktleistung und maximaler Automatisierung in die Massenfertigung überführt werden.

Mit dem Lotpastendrucker DEK Galaxy und den Bestückplattformen SIPLACE TX micron und SIPLACE CA2 stehen Elektronikfertigern leistungsfähige Lösungen zur Verfügung, um diese Marktpotenziale voll auszuschöpfen – in einem durchgängig integrierten Prozess. Präzision, Geschwindigkeit und Innovationskraft wurden hier systemübergreifend vereint – Innovationen, die nur ein Technologieführer mit tiefem Know-how in beiden Welten – der Halbleiter und der Elektronikfertigung – leisten kann.

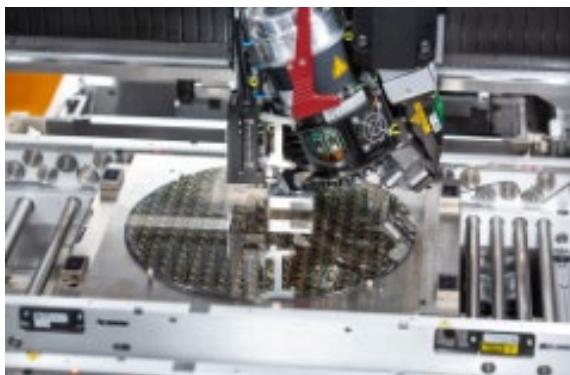

*Bestückung auf einem Wafer für Wafer Level SiP. Auch die Bestückung für WLFO Wafer Level Fan Out ist möglich.

(Bild: ASMPT)*

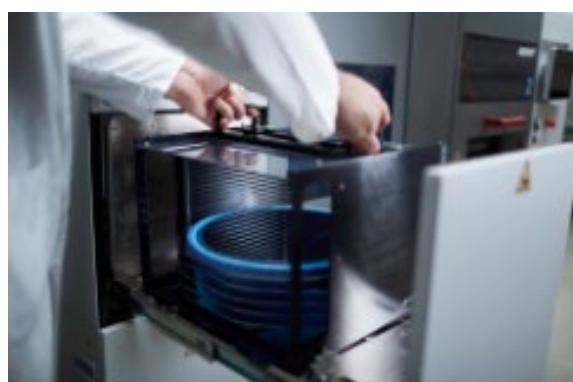

*Bestückautomat SIPLACE TX micron: Innovationssprung bei Advanced-Packaging- und High-Density-Anwendungen.

(Bild: ASMPT)*

*Automatisches Wechselsystem: Die Bestückplattform SIPLACE CA2 kann bis zu 50 verschiedene Wafer verarbeiten.

(Bild: ASMPT)*

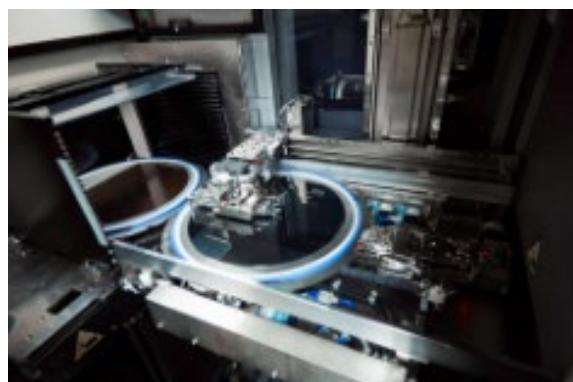

*Wafer-Transfer in die Aufnahmezone: Der Wafer Swap dauert bei der SIPLACE CA2 nur 13 Sekunden.

(Bild: ASMPT)*

*Lotpastendrucker DEK Galaxy: Performance und Präzision für SMD-Verarbeitung und Advanced Packaging.

(Bild: ASMPT)*

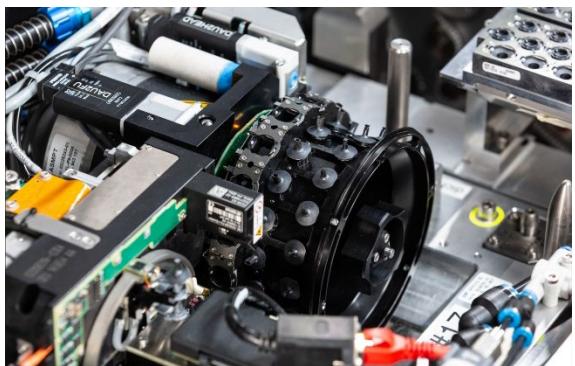

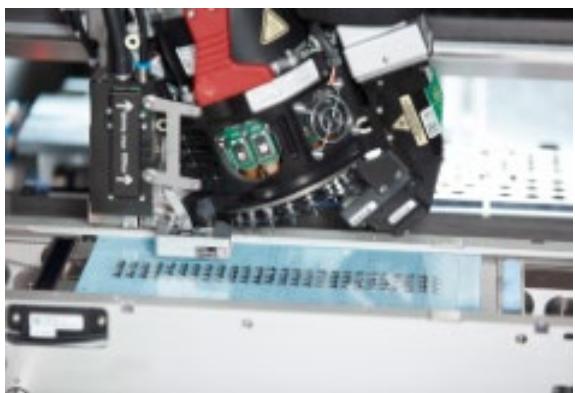

Vierfach Flip unit (links) nimmt Bauelemente vom Wafer ab mit ZwischenSpeicher für Dies (rechts): Ähnlich wie ein Collect-and-Place-Bestückkopf aufgebaut, entkoppelt der Puffer den komplexen Ablöseprozess vom Bestückvorgang und ermöglicht auch eine Die-Attach-Bestückung.

(Bild: ASMPT)

Platzierung: Die SIPLACE CA2 erreicht dank intelligenter Pufferung eine Bestückleistung von bis zu 54.000 Dies pro Stunde bei direkter Abnahme vom Wafer.

(Bild: ASMPT)

Bestückautomat SIPLACE CA2: hybride Highspeed-Verarbeitung von SMDs und Dies, direkt von Wafer.

(Bild: ASMPT)